#### **ADV DIGITAL SYSTEM DESIGN** SESSIONAL II SAMPLE EXAM

Marks: 50, (10)

#### Time: 1 Hrs

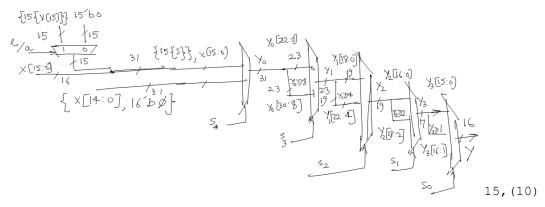

## **1.1 Question: Flow Graph Synthesis**

Write Balanced Equations for the graph and solve the equations to find a parallel HW realization of the design. Draw the realization.

1.2 Question: Digital Design with Adders

7,8

6,7,7

# a. Add the following numbers using Carry Skip Adder, clearly shows how

- logic helps in quick computation of carry, break the number in block of 3bits each

- $a = 111_{101}_{011}_{110}$

- $b = 011 \ 010 \ 100 \ 100$

- b. Design an optimal architecture of a Conditional Sum Adder to add two Qformat numbers a and b in Q1.5 and Q3.4 formats respectively. Add  $a = 1_01110$  and  $b = 101_1010$  using Conditional Sum Adder.

- c. Reduce the multi operand expression using Dadda Redcution Scheme by first representing each bit as a dot and then compression them using the scheme.

y = a + b + c + d + e + f + g

Where *a*, *b*, *c*, *d*, *e*, *f* and *g* are in Q1.2, Q1.3, Q1.4, Q1.3, Q1.5, Q2.1,Q3.1 formats respectively.

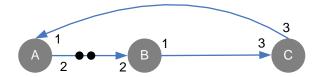

## **1.3 Question: Barrel Shifter (Take Home)**

Write RTL Verilog Code for the design of a 4-stage pipeline hierarchical Barrel shifter. This requires adding 4-pipeline registers in the following figure. (Copy the code in a separate sheet to verify the design for a number of inputs as a take home part of the exam. SUMBIT your code in next Tuesday Class)